TSMCの背面給電技術「Super Power Rail」戦略|N2P以降の技術ロードマップ

世界最大の半導体受託製造企業(ファウンドリー)であるTSMCは、背面給電技術をIntelとは異なるアプローチで開発しています。

TSMCは「Super Power Rail(SPR)」という名称で独自のBSPDN技術を推進しており、N2Pプロセス(2nm後継世代)以降での商業導入を計画しています。

Apple・NVIDIA・AMD・Qualcommなど世界最大の半導体設計企業を顧客に持つTSMCのBSPDN戦略は、半導体業界全体に甚大な影響を与えます。

本記事ではTSMCのSPR技術と今後のロードマップを詳解します。

TSMCのBSPDN戦略:慎重かつ確実なアプローチ

TSMCはIntelと異なり、BSPDN技術の導入において慎重なアプローチを採っています。

その理由は、TSMCが世界中の最重要顧客(Apple、NVIDIA、AMD等)の製品を製造しており、製造プロセスの安定性・歩留まり・コスト管理が最優先事項となっているからです。

TSMCはN2(2nm)プロセスをまずBSPDNなしで量産し、技術を安定させたうえでN2PまたはN2Xでの導入を計画するという「段階的アプローチ」を採用しています。

これはTSMCが常に採用してきた「信頼性最優先」の哲学に基づいています。

TSMCの戦略的判断

Super Power Rail(SPR)の技術的特徴

TSMCのアプローチとIntelとの違い

TSMCのSPR技術はIntelのPowerViaと同じ「裏面電源供給」という基本コンセプトを共有しながらも、実装方法に独自の差異があります。

TSMCは特に以下の点でIntelとは異なるアプローチを採用しています

| 項目 | Intel PowerVia | TSMC Super Power Rail |

|---|---|---|

| 実証時期 | 2023年(Blue Sky Creek) | 2024〜2025年(内部テスト) |

| 量産計画 | Intel 14A(2026年) | N2P/N2X(2026〜2027年) |

| 対象顧客 | Intel自社品+IFSファウンドリー | Apple、NVIDIA、AMD等外部顧客 |

| ウェハー薄化技術 | 独自バックグラインド | 独自薄化プロセス(詳細非公開) |

| ナノビア技術 | Nano TSV(詳細公開) | Backside Via(詳細非公開) |

| 情報開示姿勢 | 積極的に技術詳細を公開 | 競合情報保護のため限定的開示 |

TSMCのナノシートビア技術

TSMCはBSPDNのキー技術である「裏面ビア(Backside Via)」の形成に、NANOSHEET GAA(Gate-All-Around)トランジスタ技術との親和性を重視したプロセスを採用しているとされています。

N2世代からNANOSHEETを導入するTSMCにとって、GAAとBSPDNの統合最適化は重要な技術課題です。

TSMCのプロセスロードマップとBSPDN導入計画

N2

N2P

N2X

A16

A14

TSMCのBSPDN採用が顧客に与える影響

Appleへの影響

AppleはTSMCの最大顧客であり、iPhoneに搭載されるAシリーズSoCはTSMCの最先端プロセスを常に最初に採用してきました。

BSPDNが採用されるN2P/A16世代では、AppleのM系チップ(Mac向け)やA系チップがさらなる電力効率の向上を実現すると期待されています。

特にバッテリー駆動時間の延長とピーク性能の向上という、相反する要件の同時実現に貢献します。

NVIDIAへの影響

NVIDIAのGPU・AI加速器はデータセンターで大量の電力を消費します。

BSPDNによるIR降下の改善は、非常に大きなダイサイズのGPUチップにとって特に重要です。

大型チップほどIR降下の影響が大きく、BSPDN導入による効果も大きいためです。NVIDIA次世代アーキテクチャ(Blackwellの後継)でのTSMC BSPDN採用が注目されています。

AMDへの影響

AMDはCPU(EPYC、Ryzen)とGPU(Radeon、Instinct)の両方でTSMCの最先端プロセスを使用しています。BSPDNによる電力効率向上は、特にデータセンター向けEPYCプロセッサの競争力を高める可能性があります。

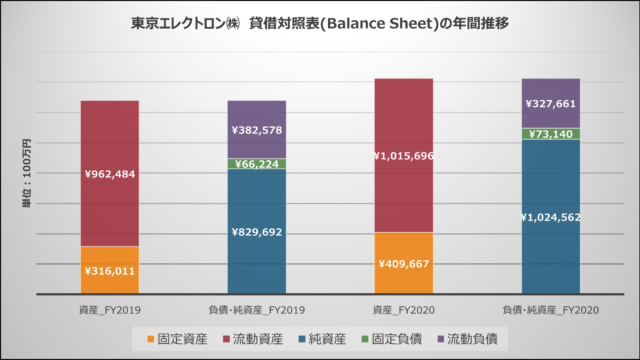

TSMCのBSPDN開発を支える装置・材料企業

TSMCのBSPDN実現には、多くの装置・材料企業との緊密な協力関係が必要です:

| 企業 | 提供技術 | 役割 |

|---|---|---|

| ASML | EUV・High-NA EUVリソグラフィ | 裏面微細パターン形成 |

| Applied Materials(AMAT) | CVD・CMP・エッチング装置 | 薄化・裏面配線形成 |

| Lam Research | エッチング・ALD装置 | ナノビア形成 |

| Tokyo Electron(TEL) | 成膜・洗浄装置 | 各種薄膜形成 |

| KLA Corporation | 検査・計測装置 | 裏面パターン検査・歩留まり管理 |

| Entegris | 特殊化学材料 | 金属薄膜・絶縁材料供給 |

TSMCが直面するBSPDN固有の課題

多品種少量生産への対応

Intelは主に自社チップを製造するIDM(Integrated Device Manufacturer)ですが、TSMCはApple・NVIDIA・AMDなど設計の全く異なる多数の顧客チップを製造するファウンドリーです。

BSPDN製造プロセスは顧客ごとにカスタマイズが難しく、標準化されたプロセスフローをどう設計するかが重要な課題です。

EDA(設計自動化)ツールの対応

BSPDNを採用したチップを設計するためには、EDA(Electronic Design Automation)ツールがBSPDNに対応している必要があります。

TSMCはSynopsys・Cadence・Siemens EDAなどと協力して、SPR対応のPDK(プロセス設計キット)とEDAフローの整備を進めています。

TSMCの強み

2025年最新動向:TSMCのA16発表

TSMCは2024年のHot Chips学会およびIEDM(International Electron Devices Meeting)において、A16プロセス(Angstromスケール世代、1.6nm相当)の詳細を発表しました。A16ではSuper Power Railを正式に採用し、GAAトランジスタとBSPDNを組み合わせることで、N2比で電力消費を15〜20%削減しつつ性能を8〜10%向上させると主張しています。

- ロジック密度:N2比で約1.1倍向上

- 性能向上:N2比で8〜10%(同電力条件)

- 電力削減:N2比で15〜20%(同性能条件)

- Super Power Rail(BSPDN)を標準採用

- 量産開始予定:2026年後半

まとめ:TSMCのBSPDNが業界に与える波及効果

TSMCがBSPDNを正式に採用・量産化すれば、その影響は業界全体に波及します。TSMCの顧客企業が生産する最終製品(スマートフォン・PC・データセンターサーバー・AI機器)すべての性能・電力効率が向上するためです。特にApple製品・NVIDIA GPU・AMD EPYCプロセッサへの採用は、数億台規模の最終製品に影響します。TSMC BSPDN商業化の2026〜2027年は、半導体アーキテクチャの転換点となる可能性が高いと言えます。