Rapidusと日本の半導体エコシステム|装置・材料・人材・研究機関の総力結集

Rapidusの挑戦を支えるのは、日本が持つ半導体エコシステムの底力です。半導体製造装置・材料・化学薬品の分野で日本企業は依然として世界トップクラスの競争力を持ちます。Rapidusが成功するためには、これらの強みをフル活用し、かつ弱点(技術者不足・設計エコシステムの薄さ)を補う必要があります。本記事では日本の半導体エコシステムとRapidusの関係を包括的に解説します。

日本の半導体エコシステムの現在地

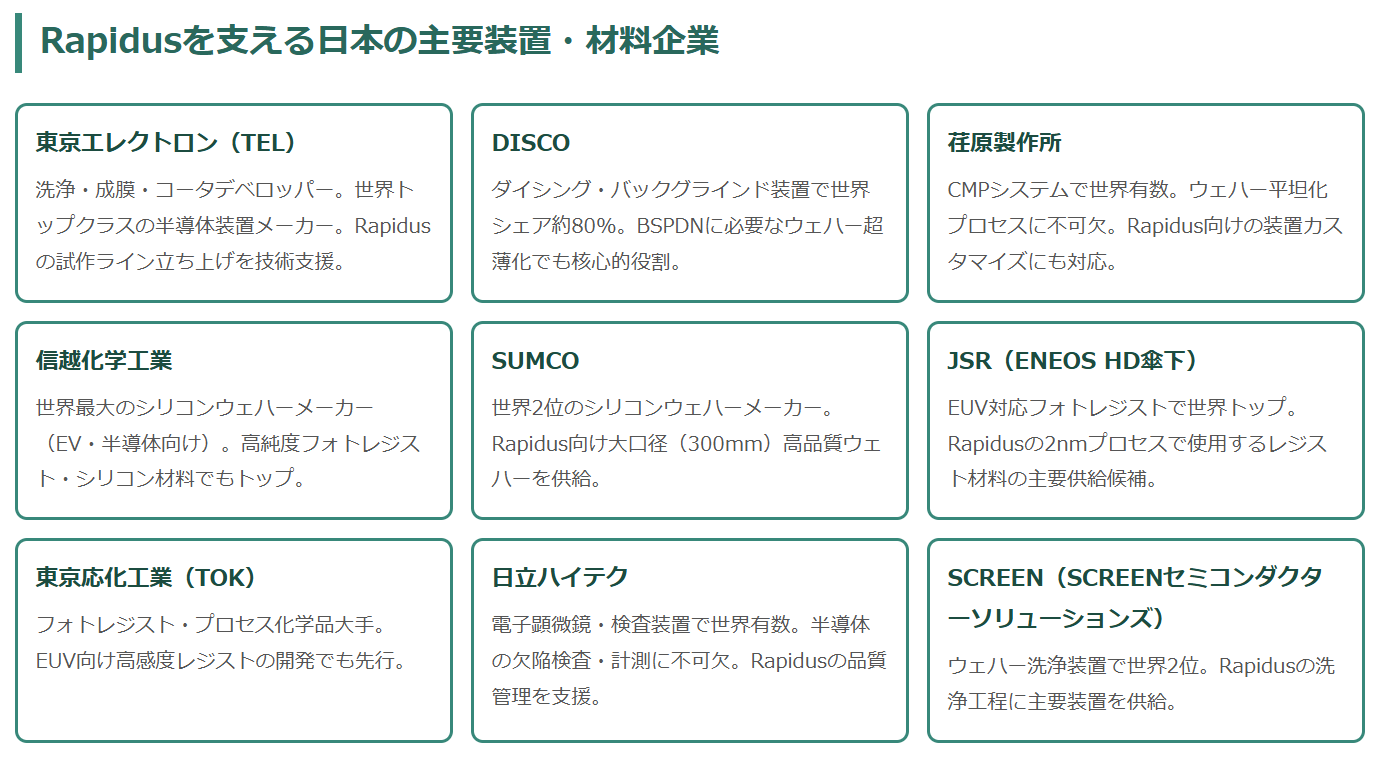

日本の半導体産業は1990年代以降、製品(ロジック・メモリ)の競争力では後退しましたが、製造を支える「基盤産業」では依然として世界をリードしています。以下の領域で日本は世界シェアの高い企業を持ちます:

Rapidusを支える日本の主要装置・材料企業

研究機関との連携:学術エコシステム

Rapidusは産学官連携のもとで半導体技術の研究開発と人材育成を進めています。日本の主要大学・研究機関との協力体制を構築しています:

人材育成:最大の課題に立ち向かう

日本の半導体産業の30年の低迷の中で、最先端プロセス(3nm以下)を扱える技術者はほとんど存在しません。Rapidusが量産に向けて必要とする人材(1,000人超)の確保は、技術・資金と並ぶ三大課題の一つです。

人材確保の方策

| 施策 | 内容 | 状況(2025年) |

|---|---|---|

| 海外人材の獲得 | TSMC・Samsung・Intel等の経験者を高給でヘッドハント | 数十人規模で獲得済み。さらなる採用継続中。 |

| Albany NanoTech研修 | IBM拠点での実地研修(数十〜百人規模) | 継続中。年間100人規模の研修を計画。 |

| 大学連携教育 | 半導体コースの新設・奨学金・インターンシップ | 北大・東北大等で半導体特化カリキュラムを展開中。 |

| 高専連携 | 高等専門学校からの早期採用・育成 | 経産省の支援でカリキュラム整備中。 |

| 中途採用(異業種) | 化学・機械・電気系技術者の転職者受け入れ・社内教育 | 社内育成プログラムを整備。 |

半導体学科・コースの新設ブーム

Rapidus効果もあり、日本の大学・高専での半導体関連教育が急速に拡充されています:

- 北海道大学:2023年に半導体特化の教育プログラムを新設。千歳を見据えた実践的カリキュラム。

- 東北大学:「半導体研究機構」を設立し、政府・産業界との三位一体で半導体研究・教育を強化。

- 東京工業大学:文部科学省の「半導体・デジタル産業戦略」の一環で半導体人材育成を強化。

- 熊本大学:TSMC誘致に合わせて半導体関連コースを拡充(Rapidusとの相乗効果も期待)。

日本の弱点:設計エコシステムの薄さ

日本のエコシステムで最も弱い部分は「半導体設計(チップ設計)」の産業集積です。米国はQualcomm・NVIDIA・Apple・AMD・Broadcomなど世界最大の「ファブレス半導体設計企業」を多数持ちますが、日本にはそのような大規模な独立系ファブレス企業がほとんどありません。

Rapidusが製造能力を持っても、そこに設計を持ち込む顧客(特に日本の設計企業)が少なければ工場が稼働できません。このため:

- 海外(米国・欧州)ファブレス企業へのアプローチが重要

- 日本のシステムメーカー(ソニー・ルネサス・キオクシア等)のチップ内製化支援

- 半導体設計スタートアップの育成支援(経産省・VCの取り組み)

- 大学発の設計プロジェクトへの製造機会提供

まとめ:日本の強みを最大活用するRapidus

日本の半導体エコシステムは「材料と装置の世界王者」という独自の強みを持ちます。Rapidusはこの強みを最大限に活用しながら、弱点である設計エコシステムと人材を急ピッチで整備しています。装置・材料・研究機関・大学・政府が一体となって支えるRapidusの挑戦は、日本の産業史上最大規模の「官民産学連携プロジェクト」と言えます。その成否は日本の次の10年の産業競争力を左右するでしょう。